티스토리 뷰

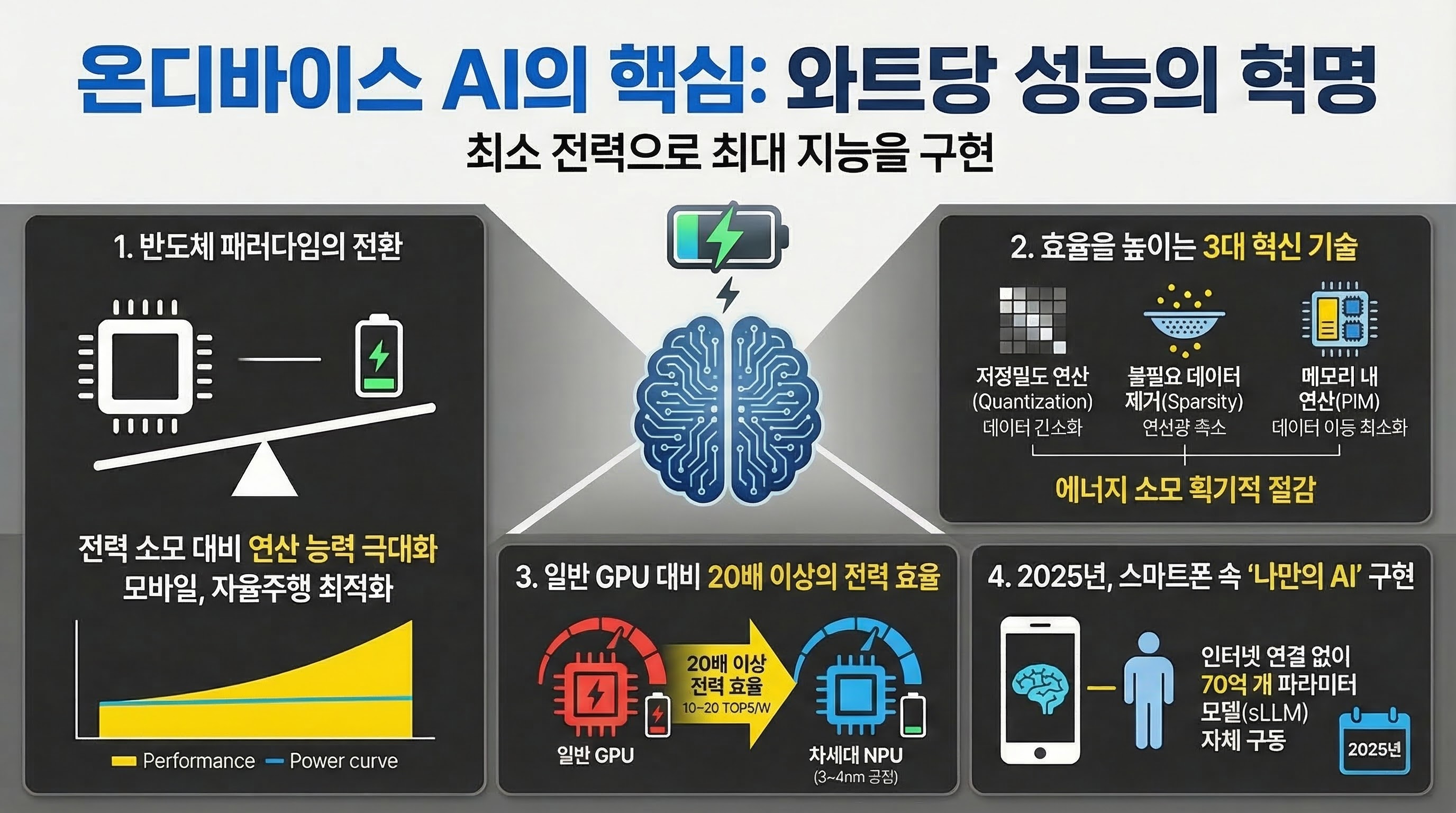

최근 전 세계 반도체 산업의 패러다임이 단순한 성능 확장에서 **'와트당 성능(Performance per Watt)'**을 극대화하는 방향으로 급격히 전환되고 있습니다. 특히 모바일 기기, 웨어러블, 자율주행차 등 전력 소모에 민감한 환경에서 복잡한 AI 연산을 수행하기 위한 **저전력 NPU(Neural Processing Unit)**의 중요성이 그 어느 때보다 강조되고 있습니다.

정부와 주요 반도체 기업들은 AI 가속기 시장의 주도권을 잡기 위해 저전력 설계 기술과 미세 공정 최적화에 막대한 자본을 투입하고 있으며, 이는 클라우드 의존도를 낮추는 온디바이스 AI(On-Device AI) 생태계 구축의 핵심적인 하드웨어 토대가 되고 있습니다.

저전력 NPU의 기술적 메커니즘과 혁신 요소

저전력 NPU는 기존의 GPU(그래픽처리장치)가 가진 범용성을 일부 포기하는 대신, 딥러닝의 핵심인 **행렬 곱셈(Matrix Multiplication)**과 **누적 연산(MAC, Multiply-Accumulate)**에 최적화된 하드웨어 가속기입니다.

1. 저전력 설계를 위한 핵심 기술

- 저정밀도 연산(Quantization): 기존 32비트 부동소수점(FP32) 연산을 8비트 정수(INT8)나 심지어 4비트(INT4) 단위로 변환하여 처리합니다. 이를 통해 메모리 대역폭 점유율을 대폭 낮추고 연산에 소모되는 에너지를 5~10배 이상 절감합니다.

- 스파시티(Sparsity) 제어: 신경망 내에서 가중치가 '0'인 데이터(유효하지 않은 데이터)를 식별하여 연산 과정에서 제외하는 기술입니다. 불필요한 데이터 이동을 차단해 전력 효율을 극대화합니다.

- PIM(Processor-In-Memory) 결합: 메모리 자체에 연산 기능을 통합하여, CPU와 메모리 사이의 데이터 병목 현상과 전력 소모를 원천적으로 줄이는 기술이 차세대 NPU에 적용되고 있습니다.

2. 하드웨어 스펙 및 공정 트렌드

최신 저전력 NPU들은 3nm(나노미터) 및 4nm 공정을 기반으로 설계되어 게이트 밀도를 높이고 누설 전류를 최소화하고 있습니다.

- 연산 성능: 모바일용 최신 NPU 기준 30~50 TOPS(Tera Operations Per Second) 이상의 성능을 구현하면서도 소모 전력은 수 밀리와트(mW) 단위까지 낮추는 것이 목표입니다.

- 아키텍처: 다층 신경망(Multi-layer Neural Network) 처리를 전용으로 담당하는 가속기 코어와 실시간 데이터 전처리를 위한 DSP(Digital Signal Processor)가 결합된 하이브리드 구조가 주를 이룹니다.

세대별 NPU 및 프로세서 전력 효율 비교

기존의 범용 연산 장치와 최신 저전력 특화 NPU의 성능 지표를 비교하면 기술적 발전 속도를 명확히 알 수 있습니다.

| 구분 | 일반 GPU (고성능) | 기존 NPU (초기형) | 차세대 저전력 NPU (현재) |

| 주요 공정 | 7nm - 5nm | 7nm | 3nm - 4nm |

| 연산 효율 (TOPS/W) | 약 0.5 - 1.0 | 2.0 - 4.0 | 10.0 - 20.0+ |

| 대기 전력 소모 | 높음 | 중간 | 매우 낮음 (Always-on) |

| 주요 데이터 포맷 | FP32 / FP16 | INT8 | INT8 / INT4 / Mixed Precision |

| 주요 적용 분야 | 데이터센터, 워크스테이션 | 초기 스마트폰 AI | 온디바이스 LLM, 웨어러블 |

산업계 배경 및 육성 히스토리

과거 AI 연산은 대부분 대규모 서버의 GPU 자원을 빌려 쓰는 클라우드 방식이었습니다. 하지만 다음과 같은 이유로 저전력 NPU를 통한 로컬 연산 능력이 필수가 되었습니다.

- 개인정보 보호: 민감한 데이터를 외부 서버로 전송하지 않고 기기 내부에서 즉시 처리해야 하는 보안 수요가 급증했습니다.

- 응답 속도(Latency): 자율주행이나 실시간 번역과 같이 초저지연 성능이 요구되는 분야에서 클라우드 통신은 한계가 있습니다.

- 지속 가능성: 수십억 대의 모바일 기기가 클라우드에 접속할 때 발생하는 데이터센터의 전력 부하와 비용을 분산시키기 위해 하드웨어단의 효율화가 절실해졌습니다.

이에 따라 주요 IT 강국들은 국가적 차원에서 반도체 보조금을 투입하고 있으며, 특히 한국의 경우 'K-클라우드 프로젝트' 등을 통해 국산 AI 반도체(NPU)의 전력 효율을 세계 최고 수준으로 끌어올리기 위한 R&D를 집중 지원하고 있습니다.

향후 로드맵 및 시장 전망

저전력 NPU 시장은 향후 5년 내 폭발적인 성장이 예상됩니다.

- 단기적 목표 (2024~2025): 스마트폰 내에서 70억 개 이상의 파라미터를 가진 소형 거대언어모델(sLLM)을 인터넷 연결 없이 구동하는 성능 확보.

- 중장기적 목표 (2026~): 인간의 뇌 구조를 모방한 뉴로모픽(Neuromorphic) 아키텍처와의 융합을 통해, 현재보다 전력 소모를 1/100 수준으로 낮추는 극저전력 기술 상용화.

업계 전문가들은 향후 반도체 시장의 승패가 "누가 더 적은 전력으로 더 복잡한 추론(Inference)을 수행하는가"에 달려 있다고 분석합니다.

출처: 삼성전자 뉴스룸, SK하이닉스 기술 블로그, 과학기술정보통신부 보도자료

원문 보기:

'IT뉴스' 카테고리의 다른 글

| 오라클, 차세대 데이터 센터 자동화 솔루션 '프로젝트 디트로이트' 공식 발표 (0) | 2026.03.19 |

|---|---|

| 삼성전자, 엔비디아 차세대 추론용 AI 가속기 위탁 생산 수주 (0) | 2026.03.18 |

| 삼성전자, 엔비디아 차세대 추론용 AI 가속기 위탁 생산 수주 (0) | 2026.03.18 |

| 엔비디아 GTC 2026: "삼성 고맙다"와 차세대 GPU '루빈' 시대의 개막 (0) | 2026.03.17 |

| 넷플릭스, 할리우드 거물 벤 애플렉의 AI 스타트업 '인터포지티브' 인수로 창작 생태계 혁신 가속화 (0) | 2026.03.13 |

- Total

- Today

- Yesterday

- Javascript

- java

- 스마트안경

- CSR

- SSR

- Rag

- AI

- 멀티모달

- sLLM

- HTML

- 협력

- CSS

- LLM

- 구글

- prompt engineering

- Nextjs

- TypeScript

- react

- 카카오

- It용어

- HBM

- MSA

- on-device ai

- 엣지컴퓨팅

- 웹기초

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 |